# AN EGRESS QUEUE MANAGER FOR 8 X 100 MBPS AND 1 X 1GBPS ETHERNET SWITCH PORT CONTROLLERS

by

#### **BARRY GORDON MOSS**

B.A.Sc., Simon Fraser University, 2002

# PROJECT SUBMITTED IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF MASTER OF ENGINEERING IN THE SCHOOL OF ENGINEERING SCIENCE

© Barry Gordon Moss 2002 SIMON FRASER UNIVERSITY December 2002

All rights reserved. This work may not be reproduced in whole or in part, by photocopy or other means, without permission of the author.

# Approval

| Name:              | Barry Gordon Moss                                                                        |

|--------------------|------------------------------------------------------------------------------------------|

| Degree:            | Master of Engineering                                                                    |

| Title of thesis:   | An Egress Queue Manager for 8 x 100 Mbps and 1 x 1 Gbps Ethernet Switch Port Controllers |

| Presentation Commi | ttee:                                                                                    |

| Chair:             |                                                                                          |

|                    | Dr. Paul Ho<br>Project Committee Chair                                                   |

|                    | Dr. Ljiljana Trajkovic<br>Senior Supervisor<br>School of Engineering Science             |

|                    | Dr. Steven Hardy Supervisor School of Engineering Science                                |

|                    | Steve Dabecki<br>External Supervisor<br>PMC-Sierra, Inc                                  |

Date approved:

#### **Abstract**

The project consists of the design of an Egress Queue Manager (EQM), a major functional block used in PMC-Sierra's PM3370 (8 x 100 Mbps) and PM3380 (1 x 1 Gbps) Ethernet Switch Port Controller integrated circuits. The EQM acts as the egress port controller in an output associated input buffered switch, providing the option of three different traffic scheduling algorithms, including variants of weighted fair queuing. While designed to operate within the environment of an Ethernet packet switch, the design is flexible enough to be adapted to other packet switched environments (such as a IP based switch) with minimal modifications.

The project consisted of the redefinition, design, verification and documentation of the EQM block, comprising approximately 70,000 gates of logic. The design was captured at the register transfer level using the Verilog hardware description language and then synthesized into a gate-level netlist. The project also includes a suite of simulations designed to verify the functionality and performance of the design, and static timing analysis to guarantee that the synthesized design was capable of operating at a clock rate of 83 MHz.

### **Dedication**

This project is dedicated to my family and friends who have encouraged me through the long process of pursuing this degree and to my former coworkers at PMC-Sierra who made this project possible. Thank you.

## Acknowledgments

Many thanks to the following individuals for their contributions to the EQM project:

Steve Dabecki at PMC-Sierra who was the technical lead in charge of the SWIT sub-section of the PM3370 and PM3380 port controller chips.

Joshua Salvador, who as an engineering co-op executed the performance simulations for the EQM design and who helped complete the second simulation test bench.

Tom Alexander from PMC-Sierra's Portland office, who invented (and re-invented) the EXACT protocol, architected the EXACT chip set, and drafted the initial EQM specification.

# **Table of Contents**

| 1 | Introd | duction                                            | 1  |

|---|--------|----------------------------------------------------|----|

| 2 | The S  | System Environment                                 | 3  |

|   | 2.1    | Port Controller Overview                           | 3  |

|   | 2.2    | The EXACT protocol                                 | 7  |

| 3 | Func   | tional Description                                 | 10 |

|   | 3.1    | Overview                                           | 10 |

|   | 3.2    | Queue Allocate/Data Block Processor (QADBP)        | 12 |

|   |        | 3.2.1 Queue Allocate Processing                    | 15 |

|   |        | 3.2.2 Data Block Processing                        | 15 |

|   |        | 3.2.3 Sequence and TPA Error Handling              | 17 |

|   | 3.3    | Transmit Pending Arrays (TPA)                      | 17 |

|   |        | 3.3.1 100 Mbps mode                                | 17 |

|   |        | 3.3.2 1 Gbps mode                                  | 18 |

|   |        | 3.3.3 Debug Access                                 | 20 |

|   | 3.4    | Queue Fetch Scheduler (QFS)                        | 20 |

|   |        | 3.4.1 100 Mbps mode                                | 22 |

|   |        | 3.4.2 1 Gbps mode                                  | 23 |

|   |        | 3.4.3 Scheduling Modes                             | 29 |

|   | 3.5    | Transmit Frame Reassembly Buffer Interface (TFRBI) | 37 |

|   |        | 3.5.1 Transmit Statistics Collection               | 38 |

|   | 3.6    | Transmit Statistics Transaction FIFO (TSTF)        | 39 |

|   | 3.7    | Statistics Updater and MPAC Interface (SUMI)       | 39 |

| 4 | Simu   | lations                                            | 42 |

|   | 4.1    | Functional Simulations                             | 42 |

|   | 4.2    | Performance Simulations                            | 43 |

| 5      | Synthesis                                | 44 |

|--------|------------------------------------------|----|

| 6      | Design reusability                       | 46 |

| 7      | System performance                       | 47 |

| 8      | A Comparison of Fair Queuing Techniques  | 48 |

| 9      | Conclusions                              | 52 |

| Apper  | ndix A: EQM Normal Register Descriptions | 53 |

| Apper  | ndix B: EQM Test Register Descriptions   | 80 |

|        | B.1 Test Mode 1: Full scan test logic    | 82 |

|        | B.2 Test Mode 2: RAM BIST                | 85 |

| Apper  | ndix C: Performance Simulation Details   | 89 |

| Refere | ences                                    | 99 |

# **Table of Figures**

| Figure 1. Partial Packet Buffer Chaining Structure. Ethernet frames are segmented and placed into queues based on the destination port and priority level. Each queue contains pointers to the first Partial Packet Buffer (PPB) of the linked list of PPBs holding a given frame                                                                                                                                                  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 2. Simplified Port Controller Block Diagram                                                                                                                                                                                                                                                                                                                                                                                 |

| Figure 3. An EXACT Based Ethernet Switch. A 24+2 Ethernet Switch created using EXACT port controllers and the ENCORE switch fabric devices. Smaller switches (e.g. an 8+1 or 16+0 switch) can be created without the switch fabric IC by connecting the EXACT Bus in a ring                                                                                                                                                        |

| Figure 4. EXACT Protocol Flow Diagram. The source device (usually an IQM) signals available traffic by sending a QA message to the destination deivce (usually an EQM). When the destination device is ready to service the QA request, it returns a QF message, allowing the source to send a single DB message. The QF/DB exchange continues until the entire packet has been transmitted across the EXACT ring or switch fabric |

| Figure 5. EQM Block Diagram. Test registers and memory BIST are not shown                                                                                                                                                                                                                                                                                                                                                          |

| Figure 6. Queue Allocate (QA) Message Format. See Table 1 for field definitions. QA messages are used to signal that an input queue has a complete packet ready to transmit to an output port associated with this EQM                                                                                                                                                                                                             |

| Figure 7. Data Block (DB) Message Format. DB messages contain packet data from a single PPB. If this is the last block of data in a given frame, the EF (end-of-frame) bit will be set. See Table 1 for field definitions. 14                                                                                                                                                                                                      |

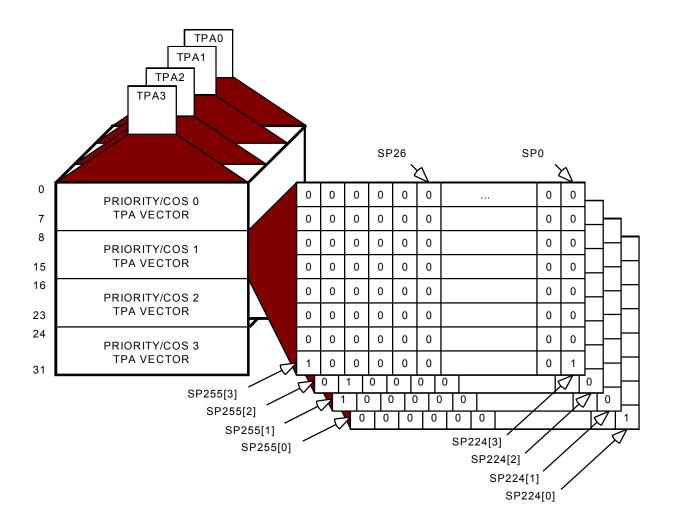

| Figure 8. The Transmit Pending Arrays configured for 8 x 100 Mbps operation. Each bit indicates if a QA has been received from a given source/priority (or class of service) queue. When the QA request has been serviced, the bit is cleared.                                                                                                                                                                                     |

| Figure 9. The Transmit Pending Arrays configured for 1 x 1 Gbps operation. Each 4-bit value indicates the number of unserviced QA messages which have been received from a given source/priority (or class of service) queue. When a QA request has been serviced, the corresponding value in the TPA is decremented. This figure illustrates an                                                                                   |

| for SPID 254 and 10 QAs for SPID 255                                                                                                                                                                                                                                                                                                     | 9   |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

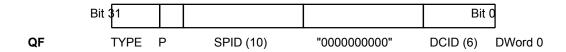

| Figure 10. Queue Fetch (QF) Message Format. QF messages are sent by the EQM to indicate that it is ready to accept a single DB message from the queue identified by the SPID and P fields                                                                                                                                                | 20  |

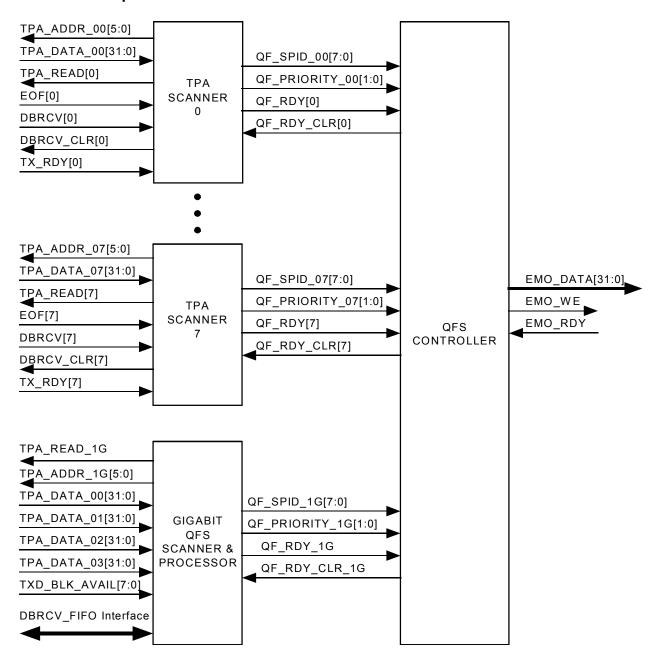

| Figure 11. Queue Fetch Scheduler Block Diagram. The QFS consists of eight TPA scanners which search the TPAs for set bits in 100 Mbps mode, a single scanner and processor which searches the TPA for non-zero QA counts in 1 Gbps mode and a controller which arbitrates between the scanners and issues the QF messages.               | 2:2 |

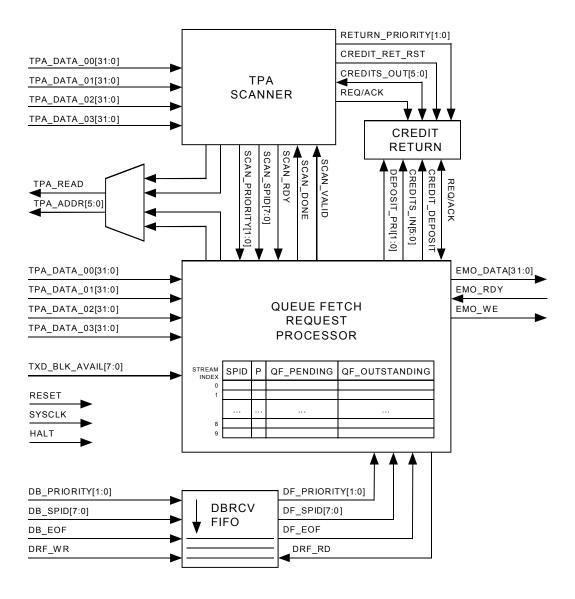

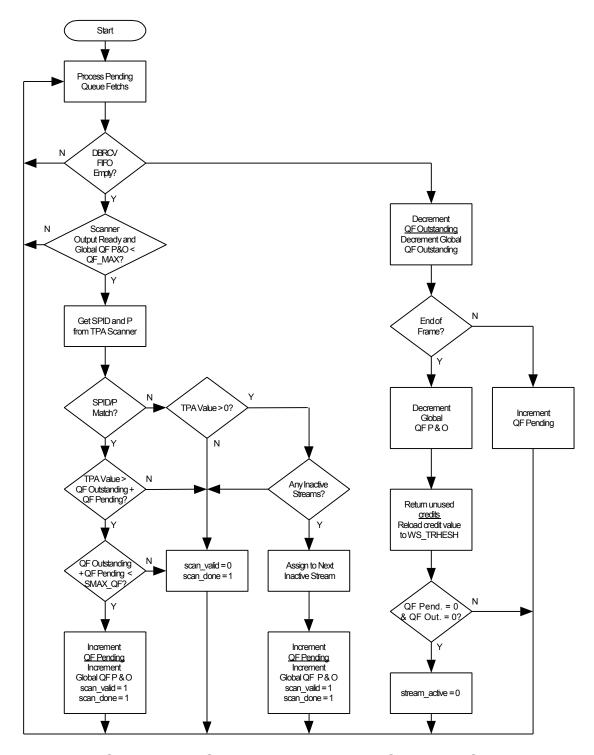

| Figure 12. Queue Fetch Scheduler: 1 Gbps Scanner and Processor Block Diagram. The QFS scans the TPA for non-zero entries and issues QF messages according to the scheduling algorithm selected and tracks the QFs pending and outstanding for each data stream.                                                                          | 24  |

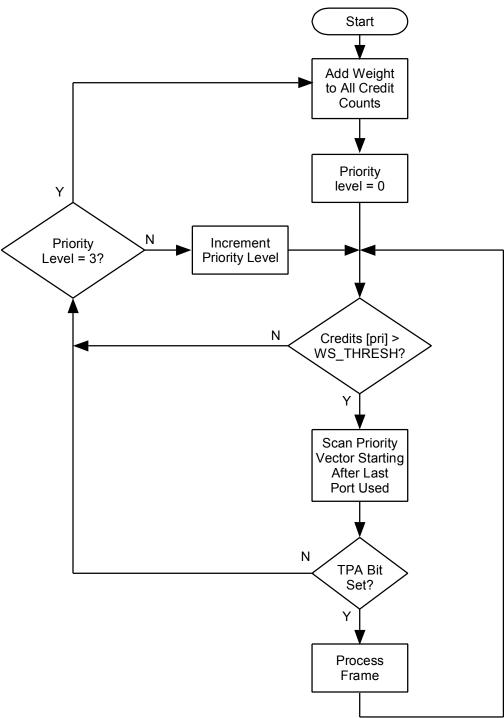

| Figure 13. Queue Fetch Scheduler Algorithm: 1 Gbps. The Queue Fetch Scheduler has a independent scanner operating in parallel which uses the same algorithms as the 100 Mbps schedulers; except that it immediately starts scanning after the decision is made to process a frame 2                                                      | 26  |

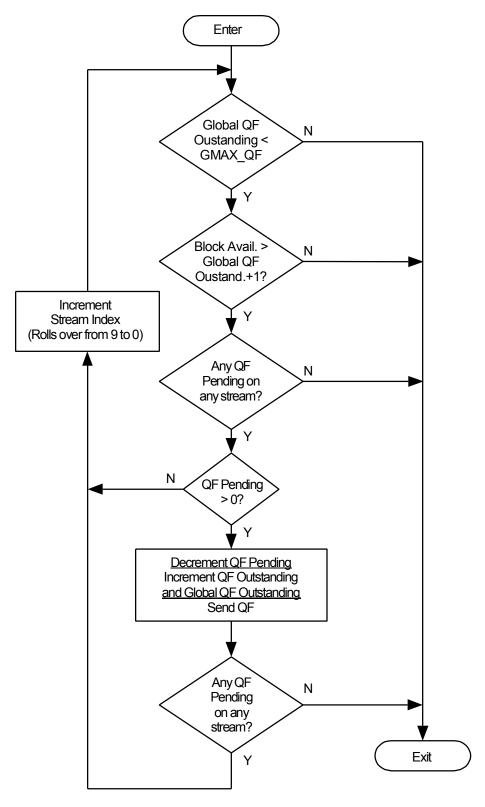

| Figure 14. Queue Fetch Pending Processing: 1 Gbps mode only 2                                                                                                                                                                                                                                                                            | 28  |

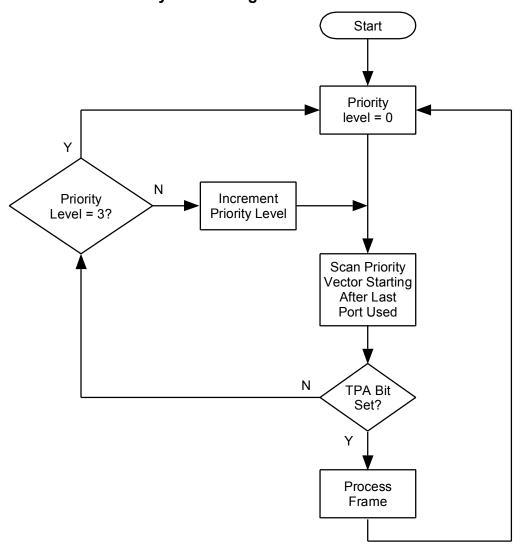

| Figure 15. Strict Priority Scheduling Algorithm. After processing each frame, SPS always checks to determine the highest priority level which has outstanding QA messages. Round robin order is maintained within each priority level. If enough traffic is presented to the high priority queues, lower priority queues can be starved. | 80  |

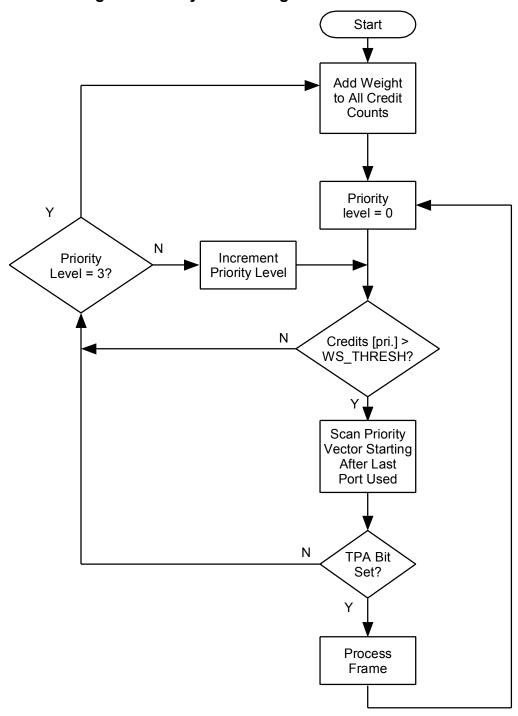

| Figure 16. Weighted Priority Scheduling Algorithm. WPS acts as a priority scheduler with credit limits to prevent starvation of lower priority queues 3                                                                                                                                                                                  | 2   |

| Figure 17. Weighted Fair Scheduling Algorithm. The WFS algorithm is very similar to the WPS algorithm: the only change is that after processing a frame, the flow jumps to the credit check instead of resetting the priority to zero as in WPS.                                                                                         | 35  |

| Figure 18. Transmit Statistics Update Transaction (TSUT) Format. The TSUT is passed from the TFRBI to the SUMI after the last byte of a frame has been passed through                                                                                                                                                                    | 89  |

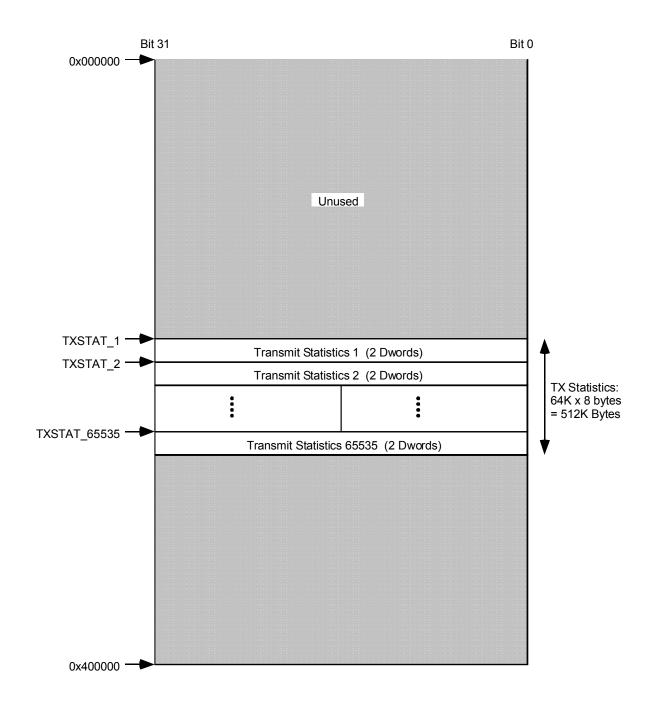

| Figure 19. Transmit Statistics Data Structure. The 2-Dword structure tracks the total number of frames and bytes transmitted in packets containing the corresponding TXSTAT field. The statistics reflect a running                                                                                                                      |     |

| prevent the counters from wrapping without being read                                                                                                                                 | 40 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

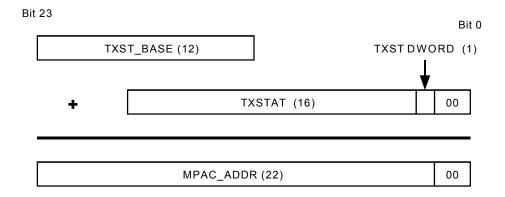

| Figure 20. SRAM Data Structure Addressing. The TXSTAT value from the TSUT is used to index into the memory block specified by TXST_BASE                                               | 40 |

| Figure 21. Example SSRAM Memory Map with 2 MByte used by EQM.  The unused portions of the memory are used by other blocks in the port controller for queue structures and statistics. | 41 |

# **Table of Tables**

| Table 1. QA and QB Message Field Descriptions.                                                         | 14 |

|--------------------------------------------------------------------------------------------------------|----|

| Table 2. QF Message Field Definition                                                                   | 21 |

| Table 3. Transmit Statistics.                                                                          | 38 |

|                                                                                                        |    |

| Table A. 1. Register 0x00: Indirect Register Select                                                    | 54 |

| Table A. 2. Register 0x01: Indirect Data                                                               | 55 |

| Table A. 3. Register 0x02: Interrupt and General Status                                                | 56 |

| Table A. 4. Register 0x03: General Control                                                             | 58 |

| Table A. 5. Scheduling Mode Control Bits                                                               | 59 |

| Table A. 6. Indirect Register 0x00: Interrupt Enable                                                   | 60 |

| Table A. 7. Indirect Register 0x01: Base Address Offset 1                                              | 62 |

| Table A. 8. Indirect Register 0x02: Illegal Source/Destination Field                                   | 63 |

| Table A. 9. Indirect Register 0x03: Illegal Message Type Field                                         | 64 |

| Table A. 10. Indirect Register 0x04: Global Maximum QF Outstanding                                     | 65 |

| Table A. 11. Indirect Register 0x05: Maximum QF Outstanding per Stream                                 | 66 |

| Table A. 12. Indirect Register 0x06, 0x09, 0x0C, 0x0F: Channel Weighted Scheduling (0-3) Limit         | 67 |

| Table A. 13. Indirect Register 0x07, 0x0A, 0x0D, 0x10: Channel Weighted Scheduling (0-3) Weight        | 68 |

| Table A. 14. Indirect Register 0x08, 0x0B, 0x0E, 0x11: Channel Weighted Scheduling (0-3) Credit Store. | 69 |

| Table A. 15. Indirect Register 0x12: Weighted Scheduling Threshold                                     | 70 |

| Table A. 16. Weighted Scheduling Threshold Values                                                      | 70 |

| Table A. 17. Indirect Register 0x20: TPA Diagnostic RAM Control Register                               | 71 |

| Table A. 18. Indirect Register 0x21: TPA Diagnostic Data High Register | . 72 |

|------------------------------------------------------------------------|------|

| Table A. 19. Indirect Register 0x22: TPA Diagnostic Data Low Register  | . 73 |

| Table A. 20. Indirect Register 0x23: QFS Stream Table Index Register   | . 74 |

| Table A. 21. Indirect Register 0x24: QFS Stream Table SPID/P Register  | . 75 |

| Table A. 22. Indirect Register 0x25: QFS Stream QF/Credit Register     | . 76 |

| Table A. 23. Indirect Register 0x26: QFS Channel Select Register       | . 77 |

| Table A. 24. Indirect Register 0x27: QFS Channel Status Register       | . 78 |

| Table A. 25. Indirect Register 0x28: QFS TXD_BLK_AVAIL Register        | . 79 |

|                                                                        |      |

| Table B. 1. Test Register 1: Test Mode Select                          | . 81 |

| Table B. 2. Test Modes                                                 | . 81 |

| Table B. 3. Test Register 0x00: Test Enable                            | . 82 |

| Table B. 4. Test Register 0x02: Scan Test Data Input.                  | . 83 |

| Table B. 5. SCAN Mode Data Output                                      | . 84 |

| Table B. 6. Test Register 0x00: Test Enable                            | . 85 |

| Table B. 7. Test Register 0x02: BIST Test Data                         | . 86 |

| Table B. 8. BIST Mode Data Output                                      | . 87 |

| Table B. 9. BIST_ERROR Bits.                                           | . 88 |

|                                                                        |      |

| Table C. 1. Perform`ance Tests Parameter Key                           | . 90 |

| Table C. 2. WFS Performance Tests – 1 Gbps mode                        | . 91 |

| Table C. 3. WPS Performance Tests – 1 Gbps mode                        | . 93 |

| Table C. 4. WFS Performance Tests – 100 Mbps mode                      | . 95 |

| Table C. 5 WPS Performance Tests – 100 Mbns mode                       | 97   |

#### 1 Introduction

The Egress Queue Manager (EQM) is a major functional block used in PMC-Sierra's PM3370 [1] (8 x 100 Mbps) and PM3380 [2] (1 x 1 Gbps) Ethernet Switch Port Controller integrated circuits. Along with PMC-Sierra's PM3390 Switch Fabric Device, these ICs form the EXACT flexible and stackable Ethernet switching architecture, capable of maintaining full line rate switching on all ports even when servicing minimum sized (64 byte) packets. The EQM operates as an 8-port single stream output scheduler controller when used in the PM3370, and operates as a single port multi-stream scheduler when used in the PM3380.

Packets are transmitted across the switch fabric in variable sized data blocks with a maximum size of 240 bytes. The EQM manages the handshaking protocol for service requests, collects transmitted data statistics and forwards the data blocks a downstream buffer for frame reassembly.

The EQM arbitrates between service requests submitted by ingress queue managers (IQM), which have traffic queued for the particular egress ports assigned to the EQM. Within a given class of service (4 are supported in the EQM), the EQM uses a simple round robin protocol. However, the EQM implements three parameterizable queuing or scheduling algorithms, which determine how bandwidth is allocated between the service classes. The simplest algorithm supported is a strict priority scheduler in which the highest service class with pending requests is always processed first. Strict priority scheduling can be used to implement the IEEE 802.1p standard [3]. The EQM also supports a weighted fair scheduling method which achieves many of the goals of the weighted fair queuing algorithm first described by Demers, Keshav and Shenkeri [4] but using a method much easier to implement in silicon. Finally, a hybrid

method, which combines features of both priority and weighted queuing, is implemented.

Within a service class, the EQM supports fair queuing (round robin) service of the individual source queues.

#### 2 The System Environment

#### 2.1 Port Controller Overview

The EQM acts as the egress controller in an output associated, input buffered switch. In this architecture, packet data is stored by an ingress queue manager (IQM) in queues corresponding to individual output ports. The ingress controller buffers a complete packet before sending a queue allocate (QA) message through the switching fabric to the EQM, where the data is destined. The switching fabric consists of one or more linked rings implementing PMC-Sierra's EXACT protocol.

The EQM does not directly access frame data as this is buffered at the ingress port, which may be on the same or a different port controller. Frame data is stored in memory as partial packet buffers (PPB's). Depending on the system configuration, each PPB contains up to 120 or 240 bytes of frame data together with header and trailer information. Independent of the size of the payload, each data block is packed into a 256 byte Partial Packet Buffer. (The 240 byte option made most efficient use of the PPB memory space; however, the 120 byte option allowed for finer granularity within the fabric). PPB's are chained together to form a linked list. The data contained in a single PPB is transmitted across the switch fabric.

The structure of the PPB's is illustrated in Figure 1.

Figure 1. Partial Packet Buffer Chaining Structure. Ethernet frames are segmented and placed into queues based on the destination port and priority level. Each queue contains pointers to the first Partial Packet Buffer (PPB) of the linked list of PPBs holding a given frame [5].

While the EQM is not protocol specific, it was implemented within an Ethernet switching system. A maximum length Ethernet frame (1522 bytes with optional VLAN tag) will require up to 14 chained PPB's to hold the complete frame, depending on the data block (DB) payload size, which is configured externally to the EQM.

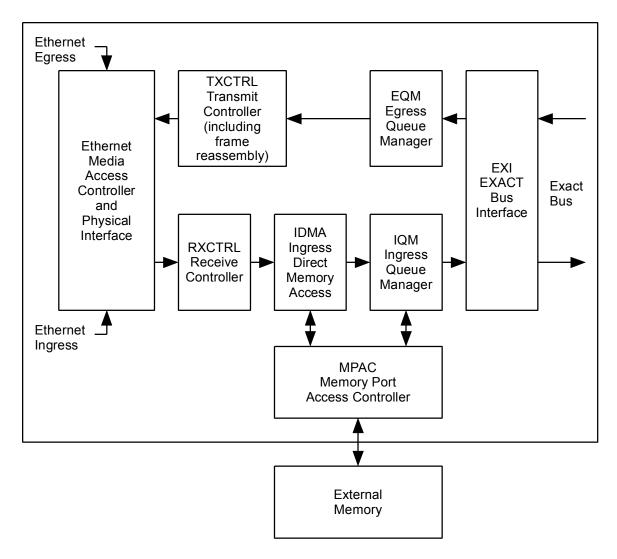

Figure 2. Simplified Port Controller Block Diagram.

Data is queued on the ingress side of the device. Control and Data messages are sent over the EXACT bus to an egress controller on the addressed port controller. Figure 2 shows a simplified block diagram or the port controller. Received Ethernet packets pass are processed by the Ethernet MAC and Receive Controller. The Ingress DMA segments the packet payloads into 240 segments and stores them in an external memory device as a chained PPB structure (see Figure 1). When a complete packet payload has been segmented into a chain of PPBs, the IDMA passes the head pointer of the chain to the

Ingress Queue Manager. The IQM places the pointer in a queue corresponding to the output port and priority (or class of service). The IQM communicates with the EQM corresponding to the egress port using the EXACT protocol (see section 2.2 following). Packet data fragments are passed through to the EQM to the Transmit Controller (TXCTRL) where the fragments are reassembled in buffers. When a complete packet has been reassembled in the TXCTRL, it is transmitted through the MAC and physical interface on the appropriate Ethernet egress port.

The EXI serves as the physical interface to the EXACT ring for the IQM and EQM, handling clock rate conversions and data path width conversions with shallow FIFOs.

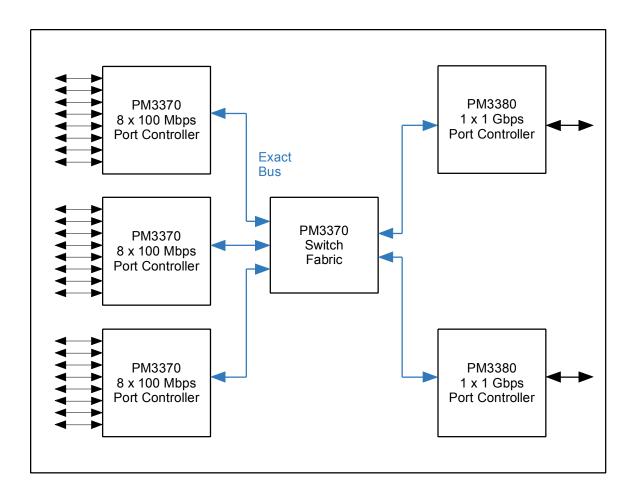

Figure 3. An EXACT Based Ethernet Switch. A 24+2 Ethernet Switch created using EXACT port controllers and the ENCORE switch fabric devices. Smaller switches (e.g. an 8+1 or 16+0 switch) can be created without the switch fabric IC by connecting the EXACT Bus in a ring.

#### 2.2 The EXACT protocol

The EXACT protocol is used to transfer data across the switching fabric, which may be a simple ring connection or a switch fabric IC.

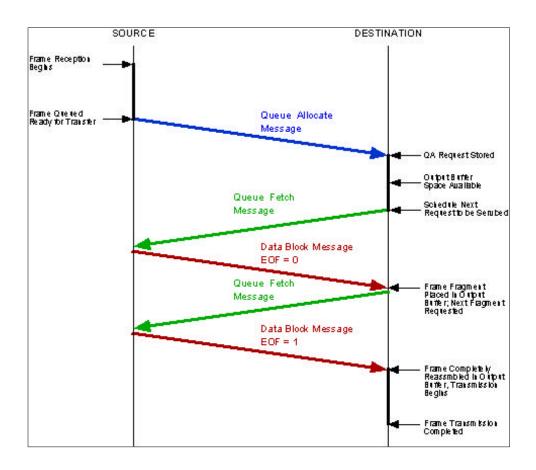

When a given IQM has queued a packet for an output port, it will send a QA message across the fabric to notify the corresponding EQM that a complete packet is available for a given output port (see Figure 4).

Figure 4. EXACT Protocol Flow Diagram. The source device (usually an IQM) signals available traffic by sending a QA message to the destination deivce (usually an EQM). When the destination device is ready to service the QA request, it returns a QF message, allowing the source to send a single DB message. The QF/DB exchange continues until the entire packet has been transmitted across the EXACT ring or switch fabric.

When the EQM is ready to accept that packet, it will send a Queue Fetch (QF) message, which allows the IQM to send a single data block (DB) message containing the first fragment of a packet, as contained in the payload of a single PPB. If there is more data in the packet, the DB message will have the EOF flag cleared in the message header. If the DB contains the end of the packet/frame, the EOF is set and the IQM may immediately send another QA message if there is one or more additional packets queued for the given output port. When the EQM receives a DB message it checks the EOF flag. If the flag is clear, the EQM

will return another QF message when it is ready to accept another DB message.

The message formats are described in greater detail later in this report.

System simulations done by the project architect showed that while this simple version of the protocol was sufficient to sustain line rates for 100 Mbps ports, the latency across the switch fabric was too great for 1 Gbps ports. Consequently, the protocol was modified for output ports operating at the higher rate.

The modified protocol allowed the IQMs to send up to 15 QA messages which would be stored by the EQMs. In return the EQM is allowed to issue up to one QF message for each QA message stored up to a maximum of 10. This allows the EWM to accept BD messages for up to 10 packets in parallel while in 1 Gbps mode. These packets could all originate from the same IQM or from multiple IQMs.

#### 3 Functional Description

#### 3.1 Overview

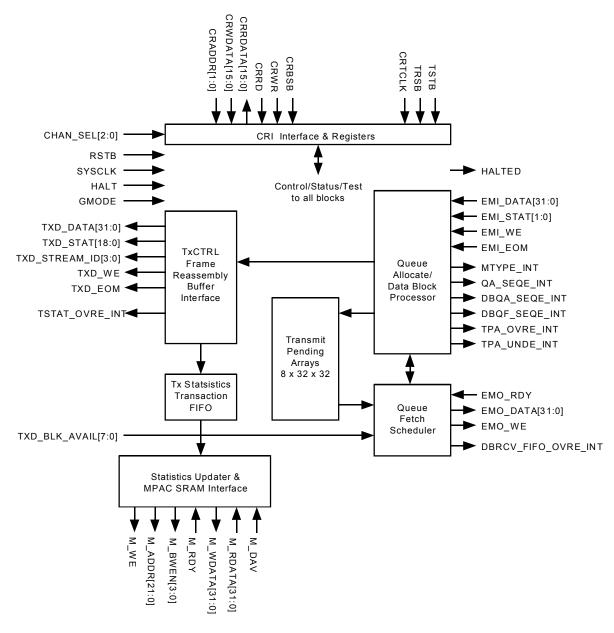

Figure 5 shows the block diagram of the EQM, which consists of the following modules:

- Queue Allocate/Data Block Processor (QADBP).

- Transmit Pending Arrays (TPAs).

- Queue Fetch Scheduler (QFS).

- Transmit Frame Reassembly Buffer Interface (TFRBI).

- Transmit Statistics Transaction FIFO (TSTF).

- Statistics Updater and Memory Port Access Controller (MPAC) SRAM

Interface (SUMI).

- Control Registers and Control Register Interface (CRI) Logic.

- Built-in Self Test (BIST) Sequencer for RAM modules.

- Test Registers and Interface Logic.

Note: The test registers and BIST circuits have been omitted from the block diagram.

A significant design goal was to reuse as much logic and in particular the TPA memories in the two operating modes (single port 1 Gbps and eight port 100 Mbps). Whenever possible, the sub-modules were designed to support both modes. This approach was successful for all blocks except the QFS which required very different designs for the two modes. Thus the QFS essentially contains two designs and the appropriate logic is enabled based on the mode selected.

Figure 5. EQM Block Diagram. Test registers and memory BIST are not shown.

#### 3.2 Queue Allocate/Data Block Processor (QADBP)

The Queue Allocate / Data Message Processor is responsible for the following:

- Receiving of queue allocate (QA) and data block (DB) messages.

- Parsing of the TYPE field within the message header to determine message type.

- Parsing of the other header fields to determine channel destination, source port, and priority/class of service.

- 100 Mbps mode: Setting the appropriate bit in the corresponding Transmit Pending Array (TPA) upon receipt of a QA message.

- 1 Gbps mode: Incrementing the appropriate 4-bit count in the Transmit Pending Array (TPA) upon receipt of a QA message.

- 100 Mbps mode: Upon receipt of a DB message, routing the payload to the TxCTRL Frame Reassembly Buffer interface (TFRBI) and setting the DB received (DBRCV) flag for the appropriate destination channel. The DBRCV flag causes the QFS to send the next QF message as soon as space is available in the corresponding downstream Transmit Frame Reassembly Buffer. If the DB header has the End of Frame (EOF) bit set, then the appropriate bit in the Transmit Pending Array is cleared, and the EOF flag for the appropriate destination channel is set. The EOF flag causes the QFS to resume the scanning the TPA for that channel according to the scheduling algorithm.

- 1 Gbps mode: Upon receipt of a DB message, routing the payload to the TxCTRL Frame Reassembly Buffer interface (TFRBI) and placing an entry in the Queue Fetch Scheduler's (QFS) DB received FIFO (DBRF) indicating the

SPID, P and EOF fields of the DB, which causes the QFS to send the next QF message (unless the EOF flag is set) as soon as space is available in the TFRBI. If the DB header has the End of Frame (EOF) bit set, then the appropriate count in the Transmit Pending Array is decremented.

The QADBP receives messages from the upstream EXI. These messages will be of two types. These will be either a queue allocate message (QA), which indicates that a source has data for one of the channels, or they will be data blocks (DB's), which contain partial data blocks constituting the complete frame. The QADBP is capable of processing a mix of QA and DB messages with minimal latency; however, the EXI must guarantee a minimum of two inactive cycles on the EMI interface between subsequent messages since the QADBP requires a minimum of 3 SYSCLKs to read-modify-write the TPA RAM.

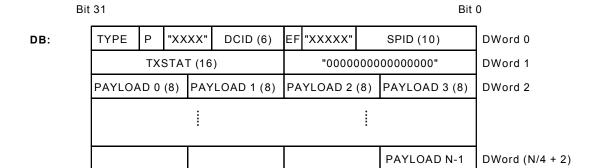

The format of queue allocate and data block messages as presented by the EXI are illustrated in Figure 6 and Figure 7 respectively. Note that the EQM only supports 256 SPIDs and 8 DCIDs. The unused most significant bits in each field (SPID[9:8] and DCID[5:3]) will always be ignored.

Figure 6. Queue Allocate (QA) Message Format. See Table 1 for field definitions. QA messages are used to signal that an input queue has a complete packet ready to transmit to an output port associated with this EQM.

Figure 7. Data Block (DB) Message Format. DB messages contain packet data from a single PPB. If this is the last block of data in a given frame, the EF (end-of-frame) bit will be set. See Table 1 for field definitions.

Table 1. QA and QB Message Field Descriptions.

| Field      | Bits | Description                                                                                                                                                                                                                                                                                                                                                                                          |

|------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TYPE       | 4    | Message Type.                                                                                                                                                                                                                                                                                                                                                                                        |

|            |      | Defines up to 16 possible message types, of which the EQM requires to know only 3: QA, QF, DB.                                                                                                                                                                                                                                                                                                       |

|            |      | 0000 - Data Block (DB)<br>0010 - Queue Allocate (QA)<br>0100 - Queue Fetch (QF)                                                                                                                                                                                                                                                                                                                      |

|            |      | Other codepoints are reserved.                                                                                                                                                                                                                                                                                                                                                                       |

| Р          | 2    | Priority of the frame.                                                                                                                                                                                                                                                                                                                                                                               |

|            |      | Every frame is allocated one of four priority levels. The IDMA passes this field on to the queue manager. The queue manager will queue the frame according to the following:                                                                                                                                                                                                                         |

|            |      | '00' - priority 0 '01' - priority 1 '10' - priority 2 '11' - priority 3 Note that priority 0 is the highest priority and priority 3 is the lowest.                                                                                                                                                                                                                                                   |

| EF         | 1    | End of Frame (EOF).                                                                                                                                                                                                                                                                                                                                                                                  |

|            |      | When EOF is set, this indicates the last data block (PPB) of the frame.                                                                                                                                                                                                                                                                                                                              |

| SPID       | 10   | Source Port Identifier                                                                                                                                                                                                                                                                                                                                                                               |

|            |      | This field indicates the EXACT ring source port from which the queue allocate was received. This field is returned as the destination port in a QF message. Note there is not necessarily a 1:1 correspondence between Ethernet ports and EXACT ring source ports. An EXACT port controller may queue frames from several Ethernet ports into a single queue which will have a single EXACT ring ID. |

| DCID       | 6    | Destination Channel Identifier.                                                                                                                                                                                                                                                                                                                                                                      |

|            |      | This field indicates the destination channel for which the queue allocate or data is intended.                                                                                                                                                                                                                                                                                                       |

| TXSTAT     | 16   | Transmit Statistics.                                                                                                                                                                                                                                                                                                                                                                                 |

|            |      | A 16-bit field which is used to index into the statistics memory.                                                                                                                                                                                                                                                                                                                                    |

| PAYLOAD    | 8+   | Data Payload.                                                                                                                                                                                                                                                                                                                                                                                        |

|            |      | This variable length field contains the packet data to be passed to the TxCTRL block. The field may vary from 1 to 240 bytes in length. The EQM does not examine or process the payload field.                                                                                                                                                                                                       |

| other bits | -    | For messages that are received by the EQM (QA and DB), bits marked as "X" are ignored.                                                                                                                                                                                                                                                                                                               |

|            |      | For messages that are transmitted by the EQM (QF), these fields are set to 0.                                                                                                                                                                                                                                                                                                                        |

|            |      | Note that some of these fields are overwritten by the upstream EXI block, to indicate a pseudo source address.                                                                                                                                                                                                                                                                                       |

The QADBP checks the header fields of the messages to first determine the type of message, and then the remaining fields to determine the subsequent processing.

#### 3.2.1 Queue Allocate Processing

A QA message indicates to the EQM that a source has data buffered for one of the channels supported by the EQM. On receiving a QA in 100 Mbps mode, the QADBP reads the appropriate line from the destination channel's TPA, sets the appropriate bit for the source port and priority/class of service, and then writes the modified line back to the TPA. In 1 Gbps mode, the QADBP reads the appropriate 4 lines from the TPAs to assemble a 4-bit count value, increments this value and then writes the modified lines back to the TPA.

In 100 Mbps mode, it is an error for the QADBP to receive a QA for a DCID/SPID/priority combination for which the QA bit is already set. In this case, the QADBP sets the QA\_SEQE\_INT interrupt flag, and places the source and destination port numbers in the appropriate error status registers.

In 1 Gbps mode, it is an error for the QADBP to receive a QA for a SPID/P combination for which TPA count has reached its maximum value of 15. In this case, the QADBP sets the TPA\_OVRE\_INT interrupt flag, and places the source and destination port numbers in the appropriate error status registers. If another TPA Overflow or sequence error occurs before the error status registers are read, the error status registers will be overwritten with the new information.

#### 3.2.2 Data Block Processing

A DB message is sent to the EQM as a result of the source port receiving a queue fetch from the EQM. On receiving a DB, the QADBP routes the data block to the TxCTRL Frame Reassembly Buffer Interface (TFRBI), which in turn writes

the data to the downstream TxCTRL Frame Reassembly Buffer (FRB). Only the payload data is transmitted to the FRB; the DB message header is removed.

The QADBP monitors the EF (end of frame) field in the data block message which indicates that this DB is the last for the frame. If this DB is not the last for the frame, then the QADBP in 100 Mbps mode immediately sets the DBRCV bit for the destination channel. If the EOF bit is set, then the QADBP clears the appropriate bit in the TPA. In 1 Gbps mode, the QADBP places an entry (including the SPID/P and EF fields) in the DBRCV FIFO of the Queue Fetch Scheduler (QFS). If the EOF bit is set, the QADBP will also decrement the corresponding count value in the TPA.

In 100 Mbps mode, it is an error for the QADBP to receive a DB for a channel which doesn't have the appropriate bit already set in its TPA, thus indicating that the DB was received without a preceding QA message or that the EOF field was set in a DB prior to the last DB for the frame. In this case, the QADBP sets the DBQA\_SEQE status flag, and places the source and destination port numbers in the appropriate error status registers.

In either mode, it is also an error for the QADBP to receive a DB for which a corresponding QF message has not been sent by the QFS. In 100 Mbps mode, the QADBP checks for this condition by comparing the SPID and P output fields of the TPA\_SCANNER for the appropriate channel. In 1 Gbps mode, the QADBP checks for this condition by comparing the DB header information against the SPID and P fields for all active streams from the QFS stream table If this error occurs, the QADBP sets the DBQF\_SEQE status flag, and places the source and destination port numbers in the appropriate error status registers.

In 1 Gbps mode, it is an error for the QADBP to receive a DB for a SPID/P combination for which the TPA has a count of 0, thus indicating that the DB was received without a preceding QA message or that the EOF field was set in a DB

prior to the last DB for the frame. In this case, the QADBP sets the DBQA\_SEQE status flag, and places the source and destination port numbers in the appropriate error status registers. If the EOF bit was set in the DB header, then the QADBP sets the TPA\_UNDE status flag, and places the source and destination port numbers in the appropriate error status registers.

#### 3.2.3 Sequence and TPA Error Handling

Sequence errors (QA, DBQA, DBQF) and TPA Overflow Underflow errors are serious protocol errors, which should occur very infrequently if ever. A single register reports the source and destination fields of the message which caused the errors is used for all error types. If another sequence error occurs before the error status registers are read, the error status registers will be overwritten with the information from the message causing the latest error. While these protocol errors were rarely if ever a problem with the production chip set, these diagnostic features proved to be invaluable while debugging the prototypes.

#### 3.3 Transmit Pending Arrays (TPA)

#### 3.3.1 100 Mbps mode

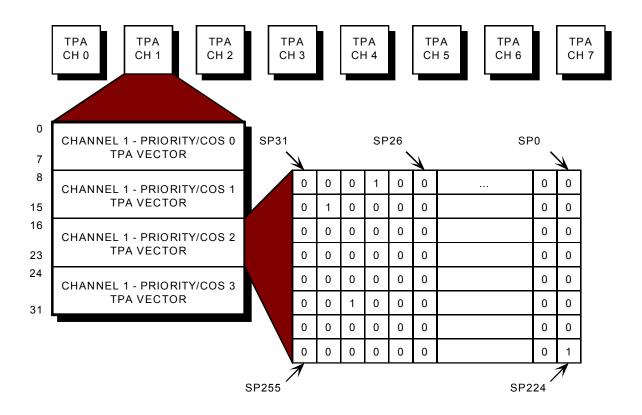

In 100 Mbps mode, there is a Transmit Pending Array (TPA) for each of the eight supported channels. Each TPA consists of four vectors, one vector for each class of service. (There is an independent TPA for each channel because all the TPA for each channel must be searched in parallel in order to meet the QA received to QF issued latency requirements). There is a single bit in the vector for each source port. Since there are a total of 256 supported source ports per vector and 4 classes of service vectors, each TPA consists of 1024 bits. (See Figure 8).

Figure 8. The Transmit Pending Arrays configured for 8 x 100 Mbps operation. Each bit indicates if a QA has been received from a given source/priority (or class of service) queue. When the QA request has been serviced, the bit is cleared.

A TPA bit is set following the receipt of a QA message for the given channel/source port/priority. A TPA bit is cleared when a DB message with an EOF indication is received for that channel/source port/priority.

The array shown above illustrates an example where destination channel 1, priority level 2, has received a QA for each of source ports 28, 62, 189 and 224.

#### 3.3.2 1 Gbps mode

In 1 Gbps mode, there is a single Transmit Pending Array (TPA) for the single supported channels. The TPA consists of four vectors, one vector for each class of service. There is a 4-bit value in the vector for each source port. The 1 Gbps TPA arrangement is illustrated in Figure 9.

Figure 9. The Transmit Pending Arrays configured for 1 x 1 Gbps operation. Each 4-bit value indicates the number of unserviced QA messages which have been received from a given source/priority (or class of service) queue. When a QA request has been serviced, the corresponding value in the TPA is decremented. This figure illustrates an example where priority level 1 has received 9 QAs for SPID 224, 8 QAs for SPID 254 and 10 QAs for SPID 255.

A TPA count is incremented following the receipt of a QA message for the given source port/priority. A TPA count is decremented when a DB message with an EOF indication is received for that source port/priority.

#### 3.3.3 Debug Access

The contents of the TPA RAMs can be accessed through the CRI for diagnostic purposes. The TPA number (0 through 7) and TPA address are programmed into the TPA Diagnostic Control Register (indirect registers). After 4 SYSCLK cycles after the TPA number and address have been written, the data word has been latched and may be read out of the TPA Diagnostic Data registers (indirect registers 0x21 and 0x22). This operation is transparent to the EQM's operation and does not require the EQM to be halted.

#### 3.4 Queue Fetch Scheduler (QFS)

The Queue Fetch Scheduler is responsible for transmitting the QF messages as a result of detecting a pending request for data as indicated in the transmit pending array (TPA) for a given channel.

The format of queue fetch message as presented to the EXI is illustrated in Figure 10. Note that the EQM only supports 256 SPIDs and 8 DCIDs. The unusued most significant bits in each field (SPID[9:8] and DCID[5:3]) will always be zeros.

Figure 10. Queue Fetch (QF) Message Format. QF messages are sent by the EQM to indicate that it is ready to accept a single DB message from the queue identified by the SPID and P fields.

The description of the various fields in the QF message are given in Table 2:

**Table 2. QF Message Field Definition.**

| Field | Bits | Description Description                                                                                                                                                                              |

|-------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TYPE  | 4    | Message Type.                                                                                                                                                                                        |

|       |      | Defines up to 16 possible message types, of which the EQM requires to know only 3, namely QA, QF, DB.                                                                                                |

|       |      | 0000 - Data Block (DB)                                                                                                                                                                               |

|       |      | 0010 - Queue Allocate (QA)                                                                                                                                                                           |

|       |      | 0100 - Queue Fetch (QF)                                                                                                                                                                              |

|       |      | Other codepoints are reserved.                                                                                                                                                                       |

| Р     | 2    | Priority of the frame.                                                                                                                                                                               |

|       |      | Every frame is allocated one of four priority levels. The IDMA passes this field on to the queue manager. The queue manager will queue the frame according to the following:                         |

|       |      | '00' - priority 0                                                                                                                                                                                    |

|       |      | '01' - priority 1                                                                                                                                                                                    |

|       |      | '10' - priority 2                                                                                                                                                                                    |

|       |      | '11' - priority 3                                                                                                                                                                                    |

|       |      | Note that priority 0 is the highest priority and priority 3 is the lowest.                                                                                                                           |

|       |      | The external CPU provides this field as part of the forwarding information.                                                                                                                          |

| SPID  | 10   | Source Port Identifier                                                                                                                                                                               |

|       |      | This field indicates the EXACT ring source port from which the queue allocate was received. This field is returned as the destination port in a QF message.                                          |

| DCID  | 6    | Destination Channel Identifier                                                                                                                                                                       |

|       |      | This field indicates the destination channel for which the queue allocate or data is intended. The upstream EXI substitutes the absolute port ID (queue ID) with the channel ID using a base offset. |

#### 3.4.1 100 Mbps mode

Figure 11. Queue Fetch Scheduler Block Diagram. The QFS consists of eight TPA scanners which search the TPAs for set bits in 100 Mbps mode, a single scanner and processor which searches the TPA for non-zero QA counts in 1 Gbps mode and a controller which arbitrates between the scanners and issues the QF messages.

The 100 Mbps QFS contains a TPA Scanner block for each channel supported. These scanners independently scan the associated TPA for set bits according the scheduling algorithm currently employed. (The TPA for each channel must be scanned independently and in parallel in order to meet the QA received to QF issued latency requirements). When a TPA Scanner detects a request for a data frame, it places the corresponding source ID and priority/class of service indication on its output and raises a flag. The QFS implements a round robin polling mechanism on the TPA Scanners and constructs the QF message when a TPA Scanner ready flag is detected, adding the relevant TYPE and DCID fields.

Once the QFS scheduling algorithm (see following section) has decided to process a given QA, the frame is processed as follows:

- Generate queue fetch for this channel, and send the QF to the indicated source port

- Wait until the QADBP sets the DBRCV (DB Message Received) flag for this channel.

- Clear the DBRCV and send another QF message for this channel, sending to relevant source port.

- Repeat until the QADBP sets the EOF (End of Frame) flag for this channel

- Return to scheduling algorithm

#### 3.4.2 1 Gbps mode

The 1 Gbps QFS supports a single destination channel, but in order to reduce the QA -> QF -> DB latency, it supports multiple outstanding QFs on multiple SPID/P traffic streams. The QFS consists of a TPA Scanner, a DBRCV FIFO and a Queue Fetch Request Processor (QFRP) as shown in figure 11.

Figure 12. Queue Fetch Scheduler: 1 Gbps Scanner and Processor Block Diagram. The QFS scans the TPA for non-zero entries and issues QF messages according to the scheduling algorithm selected and tracks the QFs pending and outstanding for each data stream.

The QFRP keeps track of the state for each of the 10 streams using a state vector consisting of the SPID/P assigned to that stream, the current number of QFs pending (i.e., assigned but pending a check of space available in the TXCTRL Frame Reassembly Buffer) and QFs outstanding (i.e., QFs which have

been issued after checking that there is sufficient space available for the resultant DB payloads).

The single TPA scanner operates very similar to the 100 Mbps mode and uses the same scheduling algorithms; however, it no longer stops and waits for an entire frame to be processed when a non-zero TPA location is encountered in the course of searching the array. Instead, the TPA Scanner passes the SPID/Priority pair to the Queue Fetch Request Processor along with the value it read form the TPA.

The QFRP will check if the SPID/P combination matches one of the data streams currently being serviced. If there is no match, the QFRP will assign the SPID/P to an unused stream if available. If no unused stream is available, then the QFRP will continue processing but will not complete the handshake with the TPA Scanner, effectively stopping scanning until a free stream is available. If the SPID/P matches the SPID/P assigned to an active steam, then the current number of outstanding (issued) QFs for the stream and the number of QFs for that same stream which are pending are checked. If the TPA count is greater than the SUM of the pending and outstanding QFs, the QFRP will increment the QF pending count and indicate that the request from the scanner is valid by asserting VALID and SCAN\_DONE; otherwise VALID is not asserted when the SCAN\_DONE indication is asserted.

If the TPA Scanners sees that its' request was valid, it will continue the scanning algorithm as in the 100 Mbps mode, treating the VALID indication as if the frame had be completely processed. If the request was not valid, then the scanner continues on as if the TPA count for the current SPID/P had been zero.

Figure 13. Queue Fetch Scheduler Algorithm: 1 Gbps. The Queue Fetch Scheduler has a independent scanner operating in parallel which uses the same algorithms as the 100 Mbps schedulers; except that it immediately starts scanning after the decision is made to process a frame.

The Queue Fetch Request Processor also services requests from the DBRCV FIFO. For each entry processed from this FIFO, the stream QF Outstanding count is decremented. If the EOF flag is not set for the entry, the stream QF Pending count is incremented. If the EOF flag is set, the QFRP checks if both the stream QF Pending and QF Outstanding counts have been reduced to zero. In this case, the stream is marked inactive and subsequently freed up for use by another SPID/P pair.

The QFRP also processes the QF Pending counts. For each stream, the QFRP checks if QF Pending is non-zero and if so checks if there is uncommitted space available in the associated frame reassembly buffer. If space is available, the stream's QF Pending count is decremented, the QF outstanding count is incremented and the QF is sent to the EXI.

The QFRP also restricts the maximum number of outstanding QFs across all streams to the value programmed in the Global Maximum QF Outstanding Register. For the PM3380 port controller, a nominal value of 10 is recommended based on system level simulations done by PMC-Sierra's chip architect, Tom Alexander. However, the value may be changed to optimize performance in other system with different fabric latencies. The value may be set as high as the maximum number of memory blocks in the TXCTRL Frame Reassembly Buffer (i.e., 70 for block size of 120 bytes, 140 for block size of 240 bytes). Setting GMAX\_QF larger than the number of blocks in the TXCTRL FRB will not permit more QFs to be issued.

Figure 14. Queue Fetch Pending Processing: 1 Gbps mode only.

# 3.4.3 Scheduling Modes

The QFS implements three modes of scheduling:

- 1. Strict Priority Scheduling (SPS)

- 2. Weighted Priority Scheduling (WPS)

- 3. Weighted Fair Scheduling (WFS)

The scheduling mode is selectable by the SCHMODE[1:0] field in the EQM General Control Register.

### 3.4.3.1 Strict Priority Scheduling

Figure 15. Strict Priority Scheduling Algorithm. After processing each frame, SPS always checks to determine the highest priority level which has outstanding QA messages. Round robin order is maintained within each priority level. If enough traffic is presented to the high priority queues, lower priority queues can be starved.

Strict Priority is a simple scheduling method. For any given egress channel, the scheduler begins by scanning the transmit pending array (TPA) for the top priority level beginning after the index of the last source port which was serviced from this priority level. If the TPA indicates that frame transmissions requests are pending, then the first such request is serviced in source port order, until the

entire data frame has been received. Additional frame requests at the top priority level are processed until all requests have been exhausted, then the vector for the next lowest priority is scanned. If there are no transmit requests pending for this priority level, the scheduler will proceed to the next lowest priority level, and repeat the scanning process. If there are transmit requests pending for this priority level, the next eligible transmit request (i.e., the request for the next port after the last port serviced) is processed and then the priority level is reset to the top priority.

# 3.4.3.2 Weighted Priority Scheduling

Figure 16. Weighted Priority Scheduling Algorithm. WPS acts as a priority scheduler with credit limits to prevent starvation of lower priority queues.

The Weighted Priority Scheduling mechanism provides the ability to distribute source data traffic over 4 weighted classes of service and prevent starvation of lower priority levels, while still maintaining a priority hierarchy.

Weighted Priority Scheduling (WPS) is implemented using a credit accumulation scheme and weighted priority servicing, requiring a total of three storage registers (weighting, credit store and credit limit) per priority level and one adder/subtracter per channel. For any given egress channel, the scheduler begins by adding the weighting value to the respective data block credit store for all priority levels. If sufficient credits are available for the highest priority level to transmit a maximum sized frame (i.e., the credit store is >= WS THRESH) then the transmit pending array (TPA) is scanned for that priority level beginning after the index of the last source port which was serviced from this priority level. If the TPA indicates that frame transmission requests are pending, then the first such request is serviced in source port order, with the credit store being decremented for each data block requested until the entire data frame has been received. Additional frame requests at the top priority level are processed so long as the credit store remains above the threshold level. When all top priority transmit requests have been exhausted or the credit store has been reduced below the threshold, the credit store for the next lowest priority level is checked and if its credit store is above the threshold level, the TPA is scanned. If there are insufficient credits available or there are no transmit requests pending for this priority level, the scheduler will proceed to the next lowest priority level, otherwise the next eligible transmit request (i.e., the request for the next port after the last port serviced) is processed and the priority level is reset to the top priority.

When all priority levels have either a credit store value below the threshold level or no transmission requests pending, the scheduler again updates the

remaining in the data block credit store. The credit store registers saturate at the limit value. The scheduler then begins again at the highest priority level.

Note that if the limit value is set to the weight value, the scheduler will be memoryless and will allocate the same share of scheduling requests each time through the loop as specified by the weighting values. However, if the limit value is larger than the weight value, then that given priority level may store its unused bandwidth up to the credit limit and the weight values become time averaged weightings. (A limit value lower than the weight value is an illegal condition since it would effectively become the weighting value).

# 3.4.3.3 Weighted Fair Scheduling

Figure 17. Weighted Fair Scheduling Algorithm. The WFS algorithm is very similar to the WPS algorithm: the only change is that after processing a frame, the flow jumps to the credit check instead of resetting the priority to zero as in WPS.

Weighted Fair Scheduling mechanism provides the ability to distribute source data traffic over n weighted classes of service.

Weighted Fair Scheduling (WFS) is implemented using a credit accumulation scheme and weighted round-robin servicing, requiring a total of three storage registers (weighting, credit store and credit limit) per class of service and one adder/subtracter per channel. For any given egress channel, the scheduler begins by adding the weighting value to the respective data block credit store for all classes of service. If sufficient credits are available for the first class of service to transmit a maximum sized frame (i.e., the credit store is >= WS THRESH) then the transmit pending array is scanned for that class of service beginning after the index of the last source port which was serviced from this class of service. If the TPA indicates that frame transmission requests are pending, then these requests are serviced in source port order, with the credit store being decremented for each data block requested until the entire data frame has been received. Additional frame requests in this class of service are processed so long as the credit store remains above the threshold level. When all transmit requests have been exhausted or the credit store has been reduced below the threshold, the next class of service is processed. When all classes of service have been serviced, the scheduler again updates the credit stores for all classes of service by adding the weighting value to the value remaining in the data block credit store. The credit store registers saturate at the limit value.

Note that if the limit value is set to the weight value, the scheduler will be memoryless and will allocate the same share of scheduling requests each time through the loop as specified by the weighting values. However, if the limit value is larger than the weight value, then bursting is allowed for that given class of service and the weight values become time averaged weightings. (A limit value

lower than the weight value is an illegal condition since it would effectively become the weighting value).

The WFS mechanism is a completely fair system which does not assign any priority to a particular class of service and simply acts as a means of sharing the available bandwidth for a channel between different class of service without wasting unused bandwidth the way traffic shapers or other bandwidth reservation systems may.

# 3.5 Transmit Frame Reassembly Buffer Interface (TFRBI)

The Transmit Frame Reassembly Buffer Interface is responsible for transferring the payload data from the DB message to the relevant TXCTRL Frame Reassembly Buffer. Only the payload data is transmitted to the downstream FIFO. (Note: the TXSTAT field from the DB header is placed on the TXCTRL interface TXD\_STAT pins at the time the payload data is transferred). The DB message header field is stripped from the data stream by the QADP. The Frame Reassembly Buffer is configured as eight virtual FIFOs for the 100 Mbps mode and as a single large pool for reassembling frames from up to ten traffic streams in the 1 Gbps mode.

The TFRBI maintains per channel/stream counts of the bytes as they are assembled in the MAC FIFOs. At the end of the complete frame, the TFRBI writes this information to the Tx Statistics Transaction FIFO.

The TFRBI does not check the status of the TXD\_BLK\_AVAIL/TXD\_RDY bus since these signals are checked by the QFS before issuing a QF.

#### 3.5.1 Transmit Statistics Collection

The EQM maintains the following transmit statistics for the each destination MAC address.

- Transmit frames total count

- Transmit bytes total count

Statistics counts are maintained in external SSRAM. The EQM receives a 16-bit pointer in each of the Data Block (DB) messages (TXSTAT) to indicate the index of the particular statistics data structure.

The update of the transmit statistics counters depend on the state of the transfer of data to the downstream Tx MAC FIFOs, after the last data block has been transmitted. Note that if TXSTAT=0, then no counters are updated. Note that the counters do not saturate but will rollover, and that it is the responsibility of system software to maintain counter integrity.

Each data structure consists of two 32-bit double words (Dwords) and contains two 32-bit counts. The TXSTAT index is used with the TXST\_BASE offset control register and the particular statistics counter being accessed, and together form a 22-bit address into external SSRAM. This is illustrated in the SUMI description later.

The various counters and their update conditions are illustrated in below:

**Table 3. Transmit Statistics.**

| Field    | Bits | Description                                                                            | Update Conditions                                                          |

|----------|------|----------------------------------------------------------------------------------------|----------------------------------------------------------------------------|

| TX_FRM   | 32   | Transmitted Frame Total                                                                | Updated at the end of the last data block if no error conditions detected. |

| TX_BYTES | 32   | Transmitted Bytes Total (Running total of bytes transmitted to the downstream TxCTRL.) | Updated at the end of the last data block if no error conditions detected. |

When the last DB for a given frame is transferred, the TFRBI places

Transmit Statistics Update Transaction (TSUT) into the Tx Statistics Transaction

FIFO (TSTF). The format of the TSUT message is as follows:

Figure 18. Transmit Statistics Update Transaction (TSUT) Format. The TSUT is passed from the TFRBI to the SUMI after the last byte of a frame has been passed through.

### 3.6 Transmit Statistics Transaction FIFO (TSTF)

The 32 entry Transmit Statistics Transaction FIFO acts as a buffer between the TFRBI and the SUMI. The TFRBI may need to capture multiple TSUTs in a very short period of time. For example, consider the extreme case where a single byte DB with EOF set for each channel is received back to back. While the SUMI module can process requests fast enough to keep up with full line rate traffic, it needs to have bursts of TSUTs buffered so that no requests are lost due to the SUNI's latency in accessing the MPAC.

### 3.7 Statistics Updater and MPAC Interface (SUMI)

The Statistics Updater and Memory Port Access Controller Interface processes the TSUT messages from the TSTF and permits the EQM to access the transmit statistics structures which are held in an external memory:

The Transmit Statistics Data Structure is stored in external memory as shown in Figure 21. There may be up to a total of 65,535 data structures. Each structure contains two 32-bit Dwords, as illustrated in Figure 19. The two Dwords are running counts of the total frames and total data bytes respectively passed through the EQM to the downstream transmit frame reassembly buffer.

Figure 19. Transmit Statistics Data Structure. The 2-Dword structure tracks the total number of frames and bytes transmitted in packets containing the corresponding TXSTAT field. The statistics reflect a running count, which must be read frequently enough by an external CPU to prevent the counters from wrapping without being read.

The data structures accessed by the SUMI and their respective addressing is illustrated in Figure 20 and Figure 21 respectively. This illustrates the case where a single 16M-bit SSRAM is used externally.

Figure 20. SRAM Data Structure Addressing. The TXSTAT value from the TSUT is used to index into the memory block specified by TXST\_BASE.

Figure 21. Example SSRAM Memory Map with 2 MByte used by EQM. The unused portions of the memory are used by other blocks in the port controller for queue structures and statistics.

### 4 Simulations

### 4.1 Functional Simulations

The functional simulations for the EQM were performed by selecting the appropriate Verilog modules in one of two test benches. These entities control/monitor the EQM I/O, and generate output files which can be checked for correct operation

The first test bench operates in a simple open loop mode, which presents individual QAs and DBs to the EQM after specified delays. This mode is used for simple tests, tests which require a specific sequence of operations, and tests for error conditions.

The second test bench implements source queue generators for each of the potentially 1024 SPID/P combinations. This mode reads in a list of frames for each source with DCID, frame length and earliest transmission time. The source mimics the behavior of an IQM block, sending QAs when the transmission time is reached and responding with DBs to each QF. When all of the scheduled frames for a given source have been transmitted, that source signals that it is finished, when all sources have finished, the test terminates. While this mode does not provide output checking, it does provide an automatic check of the EXACT protocol.

The results of simulations made with the second testbench can be analyzed using a perl script, which calculates the average BW percentage allocated to each priority (or class of service level) over the period in the simulation during which all streams at all priority levels are active.

### 4.2 Performance Simulations

A suite of simulations was created to test the performance of the EQM's WFS and WPS scheduling modes. All of these tests are run using testbench 2. The tests were carried out using varying numbers of streams (4 to 32), weights (equal ratios, arithmetic ratios and geometric ratios), limit-to-weight ratios (2:1, 3:1, 4:1), and frame sizes (64 byte tinygrams, 1522 byte maxigrams, n\*240 byte, and random) in both 100 Mbps and 1 Gbps modes. A complete list of the specific simulations executed and results are in Appendix B.

In general the EQM WFS and WPS scheduling modes were able to distribute bandwidth between the priority (class of service) levels within an error bound of +/- 2.0% of the total bandwidth. There were a few data points which lie outside this error bound; however, it was judged that the traffic distribution was accurate enough for the intended applications.

# 5 Synthesis

The EQM design was implemented in Verilog HDL code and then synthesized into a gate level netlist using Synopsys Design Compiler. The total gate count of the EQM exceeded 70,000 gates, which was a large block design for the 0.35 micron technology used to implement the port controller ICs. Theoretically, Design Compiler should have been able to synthesize the entire EQM design in a single operation. In practice the design proved to be challenging for the synthesis tool: runs took multiple days to complete and the tool was unable to meet the timing requirements. Consequently, each submodule (including top-level glue) was individually synthesized, then the submodules were assembled in a separate operation (no synthesis) and the overall timing confirmed.

The hierarchical synthesis approach yielded several benefits. First, each block was small enough that Design Compiler would complete a synthesis run in a matter of hours (instead of days). Secondly, the 100 Mbps QF scheduler could be synthesized once and then instantiated 8 times (rather than being synthesized 8 times in a top level synthesis approach). Finally if the synthesis program had difficulty meeting timing objectives for any given sub-module, it was easier to identify where the problem occurred, and make adjustments either to the sub-module architecture or the individual synthesis script and resynthesizing only the sub-module and its dependent hierarchy rather than resynthesizing the entire design.

Hierarchical synthesis did have one problem. Due to the cycle timing requirements of the design, it was not possible to place registers on the boundaries of each sub-module. Therefore, time budgeting had to be accomplished on the outputs and inputs of some sub-module. In particular, this

tended to occur when there was a large multiplexer on the output of a submodule feeding into combinatorial logic on the input of another sub-module.

Synthesis could have been made much easier by putting the multiplexer logic

into the target sub-module, leaving the source sub-module with registered

outputs. However, this approach would have created physical routing problems

with hundreds of metal layer traces needing to be routed between blocks.

Consequently, some significant effort was required to balance the timing budget

between the sub-blocks. Synthesizing the EQM as a flat entity would have

removed this issue, but as stated earlier, this approach had even more

significant problems.

# 6 Design reusability