## Microelectronics II - ENSC 325 - Spring 2022

### Textbook

ISBN 978-0-19-933913-6, 7th edition, or 8th edition, Oxford University Press

### ° Oxford Learning link to 8e resources

https://learninglink.oup.com/access/ sedra8e-student-resources#tag\_allchapters

### ° Lectures

Mondays 08:30 - 10:20, AQ 3159 Wednesdays 08:30 - 09:20, AQ 3159

### ° Tutorials

Wednesdays 09:30 - 10:20, AQ 3159

Lectures, tutorials and office hours will be on-line till Jan. 24, then back to normal

### ° Prerequisite

**ENSC 225 (Microelectronics I)**

### ° Labs

Hardware Lab - Lab 1 (after Jan. 24)

Computer Lab - circuit simulation using

LTspice ( or HSPICE in ESIL )

## Microelectronics II - ENSC 325 - Spring 2022

° Instructor

Marek Syrzycki, syrzycki@sfu.ca

Office hours: Wednesday, 13:00-14:00, ASB 8837

Teaching Assistants

Nicholaus Zilinski, nzilinsk@sfu.ca

Office hours: Thursday, 13:00 - 14:00, Lab 1

Hamidreza Ghanbari, hamidreza\_ghanbari@sfu.ca

Office hours: Tuesday, 10:30 - 11:30, Lab 1

Office hours on-line before Jan.24

° Course web page

www.sfu.ca/~syrzycki/325

user id: ENSC325

password protected

© 2015 Oxford University Press

## Microelectronics II - ENSC 325

Supplementary textbook

**Oxford University Press**

ISBN: 0195108426

Book web page

www.macs.ee.mcgill.ca/~roberts/ROBERTS/SPICE

### Microelectronics II - ENSC 325

© 2012 Oxford University Press

### Supplementary textbook

Oxford University Press, 4<sup>th</sup> Edition

ISBN: 978-0-19-544584-8

#### A note to the student

"This book has been developed for students of the engineering and technical sciences. Its purpose is to provide a framework for first conducting research and then writing clearly and comprehensively....

...This book will show you how to refine your research and writing skills so that you can present your ideas professionally both on paper and in person."

## **Microelectronics II - ENSC 325**

# **Course grading policy**

Hardware Labs (4)

50%

Quizes (4)

50%

Homework assignments (4)

not graded

Taking all quizes is mandatory. No makeup quizes are planned.

Each Lab Team in the Lab 1 will have 2 students and one parts kit.

# Hardware Lab - starts after Jan. 24

## Four experiments

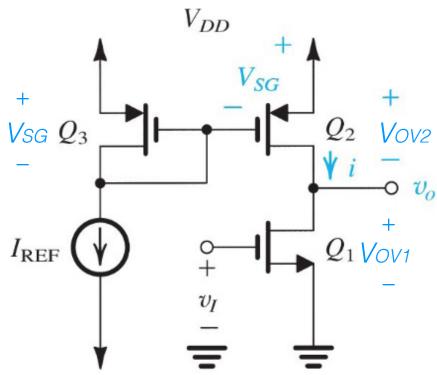

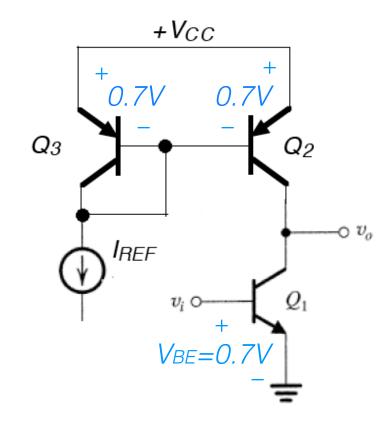

- ·· Current mirrors

- Differential amplifiers

- BJT multistage amplifier

- ·· CMOS two-stage operational amplifier

### Parts kit

| Quantity Part | Description                                                        |

|---------------|--------------------------------------------------------------------|

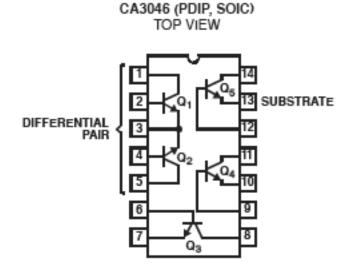

| 5 CA 3046     | General purpose NPN transistor array (5 x NPN's), Intersil, 14-PID |

| 6 2N 3904     | General purpose NPN transistor, Fairchild, TO-92                   |

| 6 2N 3906     | General purpose PNP transistor, Fairchild, TO-92                   |

| 4 2N 7000     | N-channel enhancement typo MOS FET, Fairchild, TO-92               |

| 1 LM 324      | Quad 741-type op amp, 14-Plastic Dual-In-Line                      |

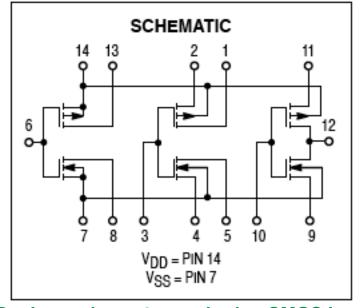

| 6 MC14007     | Dual CMOS pair plus CMOS inverter, Motorola                        |

| 2 PV36ser     | Trimpot, 200 ohms, 25 turns, MuRata, Digi-Key 490-2936-ND          |

| 2 PV36ser     | Trimpot, 1 kiloohm, 25 turns, MuRata, Digi-Key 490-2931-ND         |

| 2 PV36ser     | Trimpot, 10 kiloohm, 25 turns, MuRata, Digi-Key 490-2932-ND        |

| 2 10pF        | Capacitor, disc ceramic                                            |

| 2 33pF        | Capacitor, disc ceramic                                            |

| 2 100pF       | Capacitor, disc ceramic                                            |

| 2 330pF       | Capacitor, disc ceramic                                            |

| 2 10μF/15V    | Capacitor, electrolytic                                            |

# **Software Lab**

- LTspice software tool will be used in the ENSC 325

- downloadable to your computers from:

https://www.analog.com/en/design-center/design-tools-and-calculators/ltspice-simulator.html

- HSPICE in ESIL is available and can be also used

- Spice circuit simulator must be used with appropriate device models and/or model libraries

### npn BJT array CA3046

Differential pair plus 3 matched BJTs

### **CMOS transistor array MC14007**

**Dual complementary pair plus CMOS inverter**

# **Tentative schedule of lectures**

| Wk | Date   |   | L      | H   | Q  | Lecture Topic                                              | 7 <sup>th</sup> Ed. |

|----|--------|---|--------|-----|----|------------------------------------------------------------|---------------------|

| 1  | Jan 10 | M |        |     |    | Course overview. Current sinks and sources.                | 8.1 - 8.2           |

| 1  | Jan 12 | W |        |     |    | Simple current mirrors. Single-stage integrated amplifiers | 8.2 - 8.3           |

|    |        |   |        |     |    | with active loads.                                         |                     |

| 2  | Jan 17 | M |        | H1  |    | Cascode amplifiers. Transistor pairs.                      | 8.5, 8.7            |

| 2  | Jan 19 | W |        |     |    | Improved current mirrors.                                  | 8.6                 |

| 3  | Jan 24 | M | L1     | H1d |    | BJT differential amplifiers.                               | 9.2 - 9.4           |

| 3  | Jan 26 | W |        | H2  |    | MOS differential amplifiers.                               | 9.1                 |

| 4  | Jan 31 | M |        |     |    | Differential amplifiers with active load.                  | 9.5                 |

| 4  | Feb 2  | W |        |     | Q1 | Frequency response of differential amplifiers.             | 10.7                |

| 5  | Feb 7  | M | L1d/L2 | H2d |    | Multistage amplifiers.                                     | 9.6                 |

| 5  | Feb 9  | W |        |     |    | Output stages of op amps.                                  | 12.1 - 12.7         |

| 6  | Feb 14 | M |        | H3  |    | Simple operational amplifier (741 op amp) structure.       | 13.3                |

| 6  | Feb 16 | W |        |     | Q2 | 741 op amp analysis and parameters.                        | 13.3                |

| 7  | Feb 28 | M | L2d/L3 |     |    | Modern designs of BJT op amps.                             | 13.4                |

| 7  | Mar 2  | W |        |     |    | Power devices and power IC amplifiers.                     | 12.8 - 12.10        |

| 8  | Mar 7  | M |        | H3d |    | CMOS op amps – two-stage op amp.                           | 13.1                |

| 8  | Mar 9  | W |        |     |    | CMOS op amps – two-stage op amp.                           | 13.1                |

| 9  | Mar 14 | M | L3d/L4 |     |    | Folded cascode op amp.                                     | 13.2                |

| 9  | Mar 16 | W |        |     | Q3 | Feedback amplifiers                                        | 11.1 - 11.6         |

| 10 | Mar 21 | M |        | H4  |    | Stability of feedback amplifiers.                          | 11.7 - 11.8         |

| 10 | Mar 23 | W |        |     |    | Frequency compensation techniques.                         | 11.9 - 11.10        |

| 11 | Mar 28 | M |        |     |    | Digital logic inverters. CMOS inverter.                    | 14.2 - 14.3         |

| 11 | Mar 30 | W | L4d    | H4d |    | CMOS static logic gates.                                   | 14.1                |

| 12 | Apr 4  | M |        |     |    | CMOS pass-transistor logic circuits. CMOS dynamic          | 15.4, 15.5          |

|    |        |   |        |     |    | digital circuits.                                          |                     |

| 13 | Apr 6  | W |        |     | Q4 | Latches and registers.                                     | 16.1                |

| 13 | Apr 11 | M |        |     |    | Semiconductor memories                                     | 16.2 - 16.5         |

|    | •      |   |        |     |    |                                                            |                     |

ENSC 325 Introduction 8

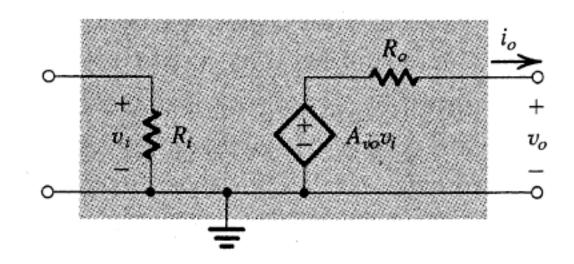

# Voltage amplifier

## **Gain Parameter**

## **Ideal Characteristics**

Open-Circuit Voltage Gain

$$A_{vo} \equiv \frac{v_o}{v_i} \bigg|_{i_o = 0} (V/V)$$

$$R_i = \infty$$

$$R_o = 0$$

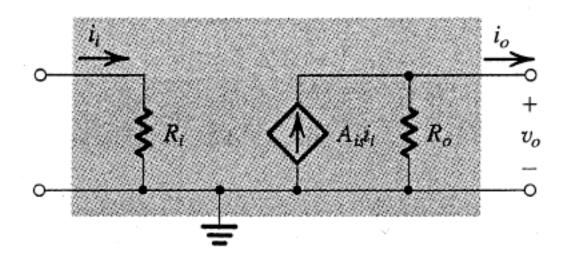

# **Current amplifier**

## **Gain Parameter**

## **Ideal Characteristics**

Short-Circuit Current Gain

$$A_{is} \equiv \frac{i_o}{i_i} \bigg|_{v_o = 0} (A/A)$$

$$R_i = 0$$

$$R_o = \infty$$

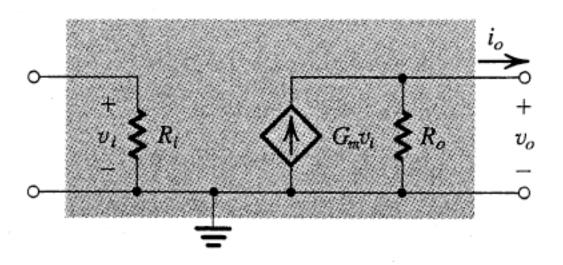

# Transconductance amplifier

### **Gain Parameter**

## **Ideal Characteristics**

Short-Circuit Transconductance

$$G_m \equiv \frac{i_o}{v_i} \Big|_{v_o=0} (\text{A/V})$$

$$R_i = \infty$$

$R_o = \infty$

ENSC 325 Introduction 13

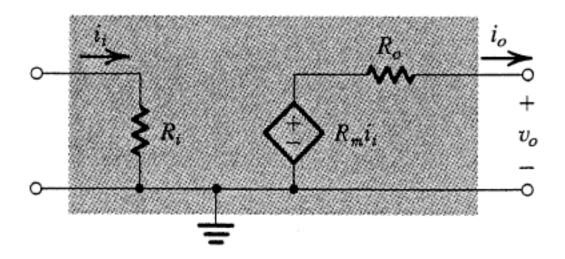

# Transresistance amplifier

### **Gain Parameter**

### **Ideal Characteristics**

Open-Circuit Transresistance

$$R_m \equiv \left. \frac{v_o}{i_i} \right|_{i_o = 0} (\text{V/A})$$

$$R_i = 0$$

$$R_o = 0$$

14

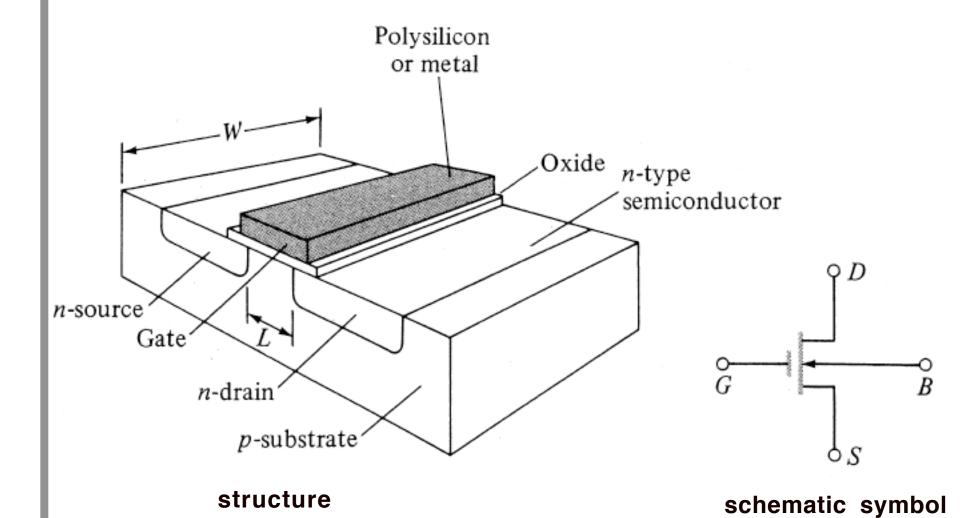

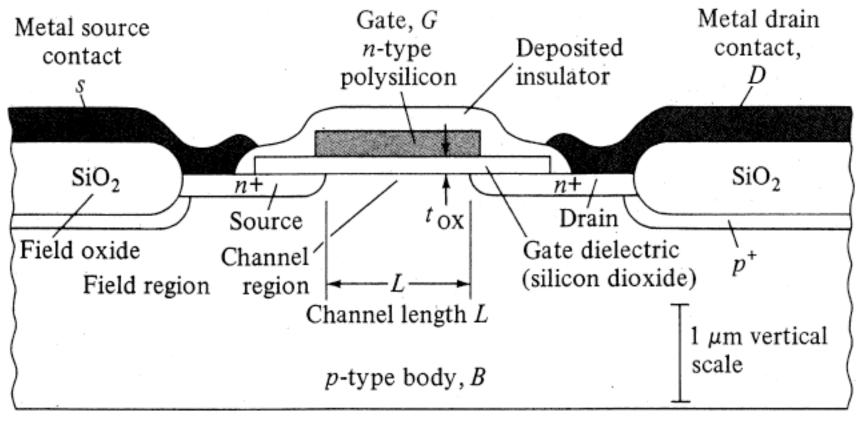

# **MOS** transistor

Source: D.A.Hodges, H.G.Jackson, Analysis and Design of Digital ICs

# **MOS** transistor

(Channel width W ⊥ to paper)

**Cross-sectional view**

5 μm horizontal scale

Source: D.A.Hodges, H.G.Jackson, Analysis and Design of Digital ICs

16

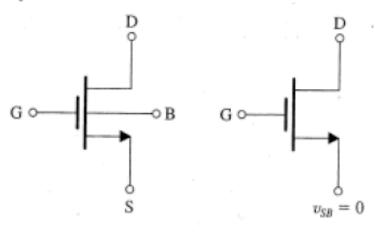

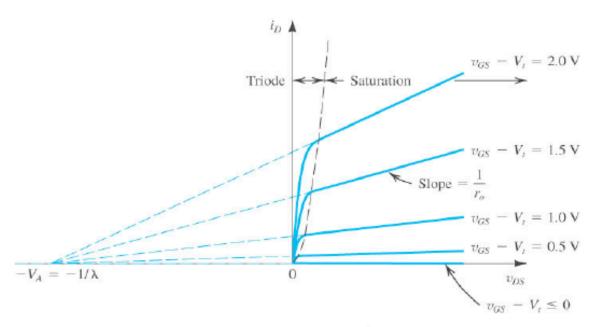

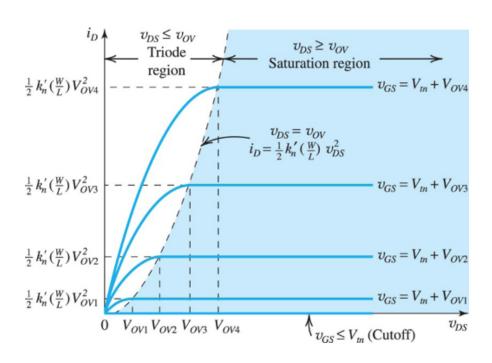

## I-V characteristics of MOS transistors

### Symbol:

### Operation in the triode region:

$$v_{GS} \ge V_t \qquad v_{DS} \le v_{GS} - V_t$$

$$i_D = \mu_n C_{ox} \frac{W}{L} \left[ (v_{GS} - V_t) v_{DS} - \frac{1}{2} v_{DS}^2 \right]$$

### Operation in the saturation region:

$$\begin{aligned} v_{GS} &\geq V_t & v_{DS} &\geq v_{GS} - V_t \\ i_D &= \frac{1}{2} \mu_n C_{ox} \frac{W}{L} (v_{GS} - V_t)^2 (1 + \lambda v_{DS}) \end{aligned}$$

### Threshold voltage:

$$V_t = V_{t0} + \gamma(\sqrt{2\phi_f + |V_{SB}|} - \sqrt{2\phi_f})$$

$$C_{ox} = \varepsilon_{ox}/t_{ox}$$

(F/m<sup>2</sup>)

$k'_{n} = \mu_{n}C_{ox}$  (A/V<sup>2</sup>)

$V'_{A} = (V_{A}/L)$  (V/m)

$\lambda = (1/V_{A})$  (V<sup>-1</sup>)

$\gamma = \sqrt{2qN_{A}\varepsilon_{s}}/C_{ox}$  (V<sup>1/2</sup>)

$\varepsilon_{0} = 8.854 \times 10^{-12} \text{ F/m}$

$\varepsilon_{ox} = 3.9\varepsilon_{0} = 3.45 \times 10^{-11} \text{ F/m}$

$\varepsilon_{s} = 11.7\varepsilon_{0} = 1.04 \times 10^{-10} \text{ F/m}$

$q = 1.602 \times 10^{-19} \text{ C}$

Introduction

Source: Sedra/Smith "Microelectronic Circuits", 7th Ed, Oxford University Press

# MOS overdrive voltage Vov

$$I_{D} = \frac{1}{2} k_{n} \left(\frac{W}{L}\right) (V_{GS} - V_{T})^{2} \left(1 + \lambda V_{DS}\right)$$

$$\lambda = 0 \longrightarrow r_{o} = \infty$$

$$V_{OV} = V_{GS} - V_{T}$$

$$i_{D} = \frac{1}{2} k_{n} \left(\frac{W}{L}\right) (V_{OV})^{2} \longrightarrow V_{OV} = \sqrt{\frac{2i_{D}}{k_{n}} \left(\frac{W}{L}\right)}$$

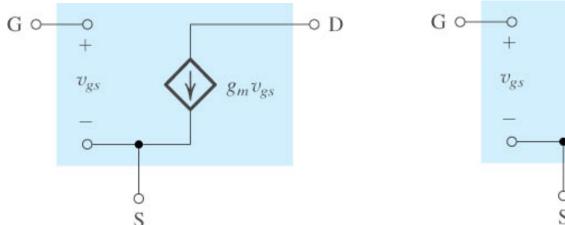

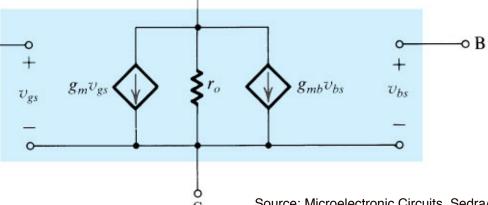

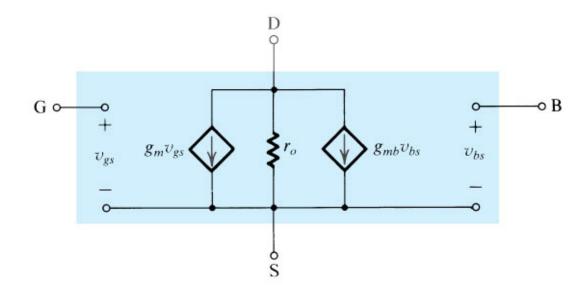

# **Small-signal models of MOS transistor**

neglecting channel-length modulation effect (output resistance  $r_0 = \infty$ )

including channel-length modulation effect (finite output resistance r<sub>o</sub>)

G o-

$G \circ \longrightarrow \circ \longrightarrow \circ D$   $v_{gs} \longrightarrow g_m v_{gs} \nearrow r_o$  S

including channel-length modulation effect and substrate (bulk) transconductance g<sub>mb</sub> (v<sub>bs</sub> ≠ 0)

D

Source: Microelectronic Circuits, Sedra/Smith, 5<sup>th</sup> ed.

# Small-signal model and parameters of MOS transistor

model

parameters

transconductance

$$g_m = \mu_n C_{ox} \frac{W}{L} V_{OV} = \sqrt{2\mu_n C_{ox} \frac{W}{L} I_D} = \frac{2I_D}{V_{OV}}$$

substrate (bulk) transconductance

$$g_{mb} = \chi g_m = \frac{\gamma}{2\sqrt{2\phi_f + V_{SB}}}g_m$$

output resistance

$$r_o = V_A/I_D$$

Source: Microelectronic Circuits, Sedra/Smith, 5th ed.

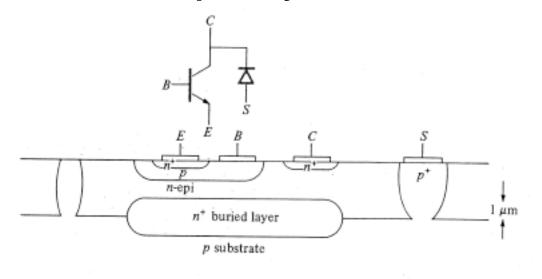

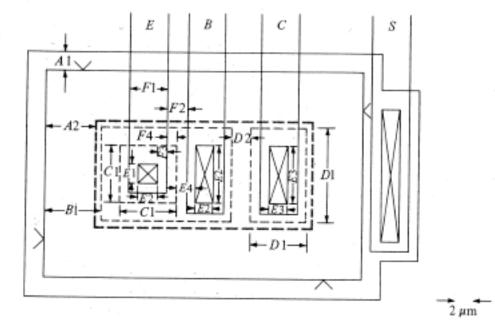

# **Bipolar junction transistors (BJTs)**

Integrated circuit npn transistor structure

**Cross-sectional view**

### Layout

Buried-layer mask \_\_\_\_\_\_

Isolation mask \_\_\_\_\_\_

Diffusion mask \_\_\_\_\_\_

Metal mask \_\_\_\_\_\_

Contact window mask 🄀

Source: D.A.Hodges, H.G.Jackson, Analysis and Design of Digital ICs

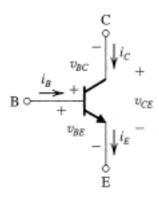

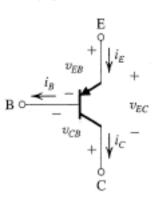

# **Bipolar junction transistors (BJTs)**

#### Circuit Symbol and Directions of Current Flow

#### npn Transistor

#### pnp Transistor

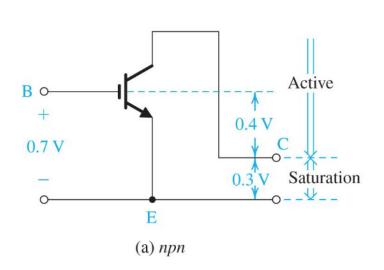

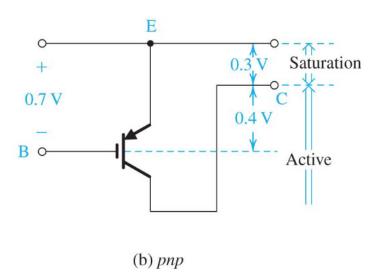

#### Operation in the Active Mode (for Amplifier Application)

#### Conditions:

$$v_{BE} > V_{BEon}$$

;  $V_{BEon} \equiv 0.5 \text{ V}$

$$v_{EB} > V_{EBon}$$

;  $V_{EBon} \equiv 0.5 \text{ V}$

Typically,

$$v_{BE} = 0.7 \text{ V}$$

Typically,

$$v_{EB} = 0.7 \text{ V}$$

$$v_{BC} \le V_{BCon}$$

;  $V_{BCon} \equiv 0.4 \text{ V}$

$\Rightarrow v_{CE} \ge 0.3 \text{ V}$

$$v_{BC} \le V_{BCon}$$

;  $V_{BCon} \equiv 0.4 \text{ V}$   $v_{CB} \le V_{CBon}$ ;  $V_{CBon} \cong 0.4 \text{ V}$

$\Rightarrow v_{EC} \ge 0.3 \text{ V}$   $\Rightarrow v_{EC} \ge 0.3 \text{ V}$

Current-Voltage Relationships

$$= i_C = I_S e^{v_{BE}/V_T}$$

$$I_C = I_S e^{v_{EB}/V_T}$$

$$i_E = i_C/\alpha \iff i_C = \alpha i_E$$

$$\beta = \frac{\alpha}{1-\alpha} \iff \alpha = \frac{\beta}{\beta+1}$$

A = emitter area

$$I_S = A \cdot I_S$$

# BJT base-emitter voltage VBE [VBE(ON)]

### BJT biased in active region:

**B-E junction forward biased**  $\longrightarrow$   $V_{BE} = V_{BE(ON)} = 0.7V$

B-C junction reverse biased (or forward biased below 0.4V)

### **BJT** biased in saturation region:

Both junction froward biased -  $V_{CE} \le 0.3V$

Introduction

24

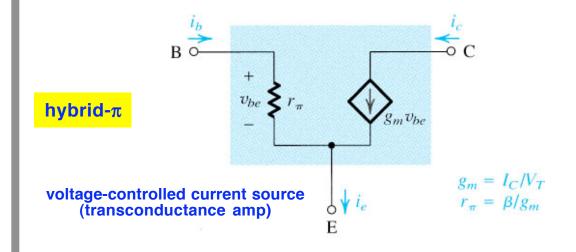

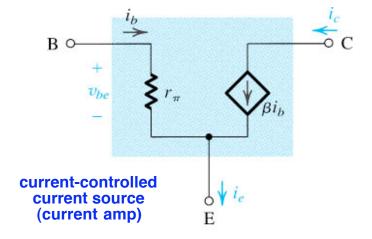

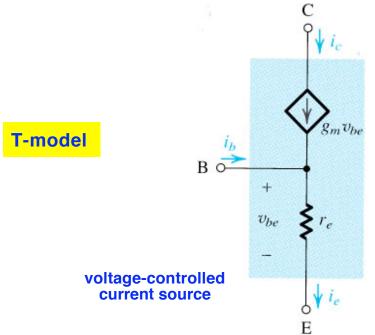

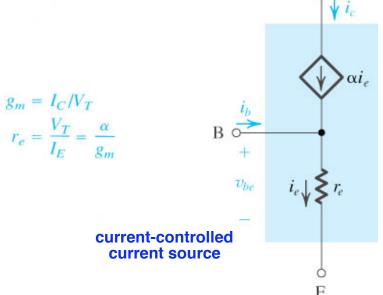

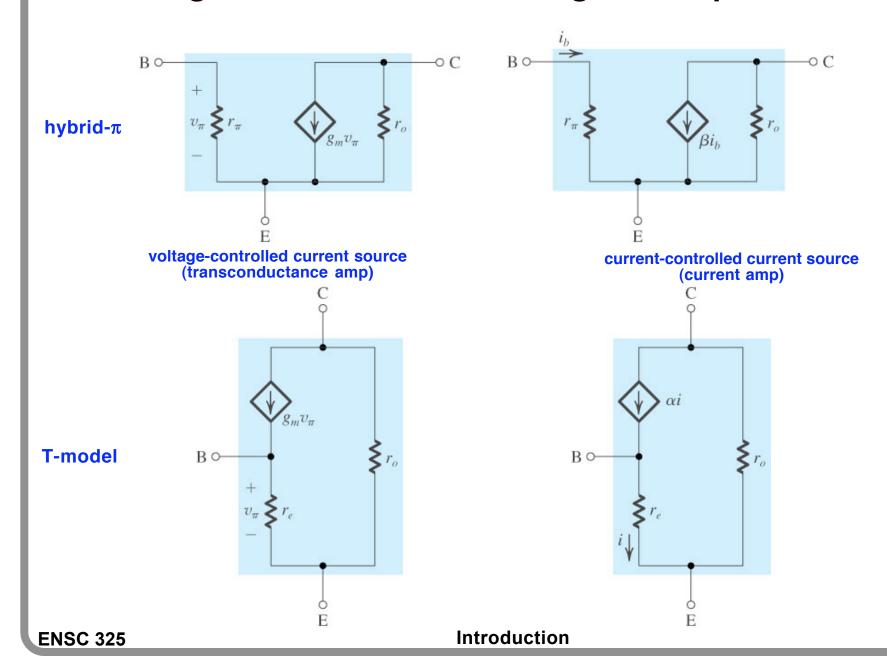

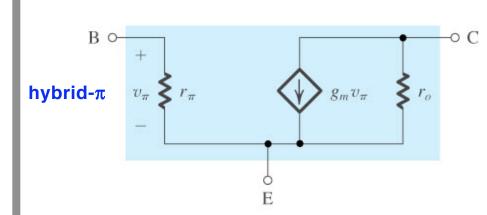

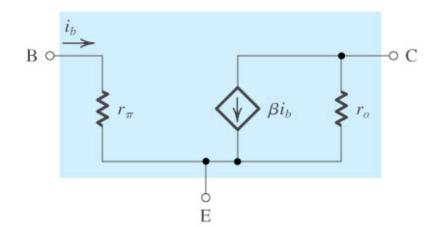

# Small-signal BJT model including the output resistance

## **Small-signal BJT model parameters**

Model Parameters in Terms of DC Bias Currents

$$g_m = \frac{I_C}{V_T}$$

$$r_e = \frac{V_T}{I_E} = \alpha \left(\frac{V_T}{I_C}\right)$$

$$g_m = \frac{I_C}{V_T}$$

$r_e = \frac{V_T}{I_E} = \alpha \left(\frac{V_T}{I_C}\right)$   $r_\pi = \frac{V_T}{I_R} = \beta \left(\frac{V_T}{I_C}\right)$   $r_o = \frac{|V_A|}{I_C}$

$$r_o = \frac{|V_A|}{I_C}$$

In Terms of  $g_m$

$$r_e = \frac{\alpha}{g_m}$$

$r_\pi = \frac{\beta}{g_m}$

$$r_{\pi} = \frac{\beta}{g_m}$$

In Terms of r.

$$g_m = \frac{\alpha}{r_s}$$

$$r_{\pi} = (\beta + 1)r$$

$$g_m = \frac{\alpha}{r_e}$$

$r_\pi = (\beta + 1)r_e$   $g_m + \frac{1}{r_\pi} = \frac{1}{r_e}$

Relationships Between  $\alpha$  and  $\beta$

$$\beta = \frac{\alpha}{1 - \alpha}$$

$$\alpha = \frac{\beta}{\beta + 1}$$

$$\beta = \frac{\alpha}{1-\alpha}$$

$\alpha = \frac{\beta}{\beta+1}$   $\beta+1 = \frac{1}{1-\alpha}$